# M830 Series

12.249Gb/s 0C-192 Clock & Data Recovery Transmitter Module

# FEATURES

- Superior PLL-based jitter performance

- 8psec p-p jitter

- **0.9Vp-p complementary data outputs**

- **1** UI externally adjustable clock phase

- 200mVp-p input sensitivity

- Optional adjustable bias @ data input to decision circuit

- Externally adjustable decision threshold

#### APPLICATIONS

SONET OC-192 and SDH STM Physical Layer and Clock and Data Recovery Applications Incorporating Forward Error Correction

#### DESCRIPTION

The M830 Series CDR module is specifically designed to regenerate the spectral clock component from an incoming NRZ data stream, incorporating forward error correction, and output a low-jitter clock and retimed complementary data.

The module utilizes a phase-locked loop architecture incorporating a high-stability, low noise SAW VCO to provide extremely low jitter clock and data outputs. The incoming data is frequency doubled to recover the clock component. The clock signal is then filtered by a microwave band pass filter to remove wide band noise and spurious signal. This signal is further filtered using the narrow band SAW VCO based PLL to minimize the noise close to the carrier. The low jitter clock is then used to retime the data and serves as the module's clock output. The module provides usercontrolled clock phase shifter and output data crossover adjustments to optimize system performance.

PLL lock-in range and loop transfer characteristics are optimized for minimal jitter in accordance with ITU and Bellcore standards for SONET/SDH systems.

## **ABSOLUTE MAX RATINGS**

| Operating Temp. Range (Case) 0°C to +70°C   |  |  |  |  |  |

|---------------------------------------------|--|--|--|--|--|

| Storage Temp. Range (Ambient)40°C to +125°C |  |  |  |  |  |

| Power Supply Voltage                        |  |  |  |  |  |

| Vcc:+5.25Vdc                                |  |  |  |  |  |

| Vee:5.25Vdc                                 |  |  |  |  |  |

| Ref Voltage+0.3 to -1.6V                    |  |  |  |  |  |

| Phase Shift Control0 to +15V                |  |  |  |  |  |

# SPECIFICATIONS

Specifications @ Vcc = +5.0 Volts, Vee = -5.0 Volts, Data in =  $2^{31}$ -1 PRBS NRZ, Mark ratio = 1:2, and T<sub>A</sub> = +25°C unless otherwise specified

| PARAMETER                          | Min   | Тур     | Max   | Units    | Condition                             |

|------------------------------------|-------|---------|-------|----------|---------------------------------------|

| Data Rate                          |       | 12.2493 |       | Gb/s     | NRZ                                   |

| Data Input Level                   | 200   |         | 600   | mVp-p    | Single-ended, $50\Omega$ , AC coupled |

| Data Input Return Loss             |       | 10      | 12    | dB       | 50MHz to 7GHz                         |

| Data Output Voltage                | 750   | 900     | 1100  | mVp-p    | Data & Data                           |

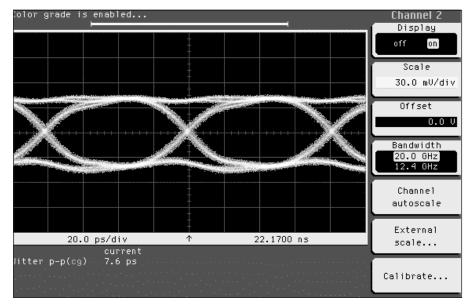

| Data Output Jitter                 |       | 7.5     | 10    | psec p-p | 2 <sup>7</sup> –1 PRBS NRZ            |

| Data Output Duty Cycle Distortion  |       | 2.5     | 5     | %        |                                       |

| Data Output Rise Time (20% to 80%) |       | 25      | 35    | psec     | $50\Omega$ , AC coupled               |

| Data Output Fall Time (80% to 20%) |       | 25      | 35    | psec     | $50\Omega$ , AC coupled               |

| Data Output Return Loss            | 10    | 12      |       | dB       | 50MHz to 9GHz                         |

| PLL Loop BW                        |       | .3      |       | MHz      |                                       |

| Decision Threshold Control         | 10    |         | 90    | %        | Relative to max Data Input Voltage    |

|                                    |       |         |       |          | Ref -0.2 to -0.75V                    |

| Decision Threshold Control         |       |         |       |          |                                       |

| Voltage Range                      | -0.75 |         | -0.2  | Volts    | Internal load of $45\Omega$ to -0.45V |

| Clock Output Level                 | 800   | 1200    | 1400  | mVp-p    | $50\Omega$ , AC coupled               |

| Clock Phase Control                | 1     |         |       | UI       |                                       |

| Clock Phase Control Voltage        | 0     |         | +15   | Volts    | $10k\Omega$ , minimum load impedance  |

| Clock SSB Phase Noise              |       |         |       |          |                                       |

| @100Hz Offset                      |       | -70     |       | dBc/Hz   | 2 <sup>31</sup> –1 PRBS NRZ           |

| @1kHz Offset                       |       | -85     |       | dBc/Hz   |                                       |

| @10kHz Offset                      |       | -90     |       | dBc/Hz   |                                       |

| Clock Jitter                       |       | 7.5     | 9     | psec p-p | 2 <sup>7</sup> –1 PRBS NRZ            |

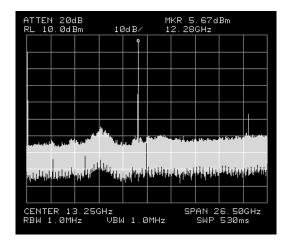

| Spurious Output                    |       | -50     |       | dBc      |                                       |

| Harmonic Output                    |       | -30     |       | dBc      |                                       |

| Supply Voltage                     |       |         |       |          |                                       |

| Vcc                                | +4.75 | +5.0    | +5.25 | Volts    |                                       |

| Vee                                | -5.25 | -5.0    | -4.75 | Volts    |                                       |

| Supply Current                     |       |         |       |          |                                       |

| lcc                                |       | 450     | 600   | mA       |                                       |

| lee                                |       | 300     | 550   | mA       |                                       |

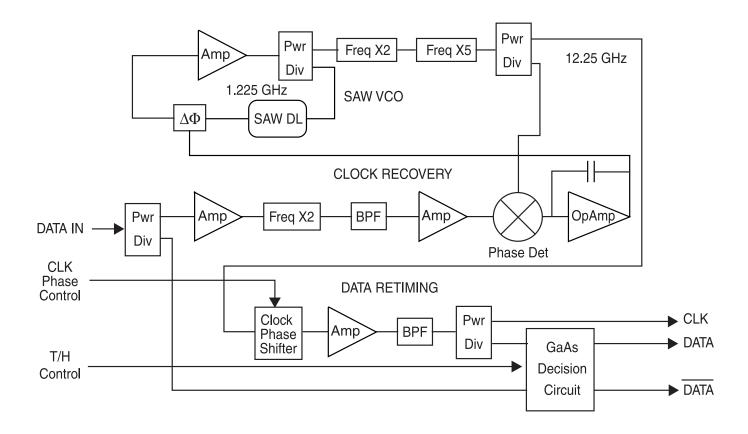

# **BLOCK DIAGRAM**

The M830 clock and data recovery module has a SAW VCO based phase-locked loop architecture. The 1.225GHz fundamental VCO is implemented as a transmission oscillator. The oscillator loop includes the SAW resonator that has a linear phase with frequency characteristic, a linear voltage controlled phase shifter, loop amplifier, and power divider to couple signal from the loop. The oscillator is frequency doubled to 2.450GHz and band pass filtered. The 2.450GHz is then multiplied by five to the final frequency of 12.25GHz. The output of the VCO is power divided to provide an input to the phase detector and a clock signal.

The input data is power divided to provide inputs to the decision circuit and the clock recovery circuitry. The input to the clock recovery circuit is amplified and applied to an analog frequency doubler to extract a clock spectral component from the NRZ data input stream. The 12.25GHz doubler output is band pass filtered and amplified.

One VCO output and the clock extracted from the input data serve as inputs to a microwave phase detector. The phase detector output is applied to an

integrator circuit. The integrator output controls the phase shifter in the SAW VCO, completing the phaselock loop. The phase-locked loop causes the low noise VCO output to be phase-locked to the clock signal extracted from the NRZ input data, providing a low jitter clock signal.

The clock signal is applied to a phase shifter that allows the timing between the input data and clock to be adjusted for optimum performance. The phase shifter output is amplified and band pass filtered to provide a low jitter and low spurious clock. The clock is power divided to provide the clock output of the module and the clock input to the decision circuit.

The decision circuit is a high speed D flip-flop. In addition to the clock and data inputs, a user adjustable decision threshold voltage is available. This voltage is used to optimize the retimed data. The CDR threshold and phase shifter do not require adjustment over the temperature and input data level ranges.

The clock output of the CDR is a low spurious sinusoidal signal and the complementary data outputs are AC coupled ECL signals. DC coupled ECL compatible data outputs are available.

# DATA OUTPUT EYE DIAGRAM

Data Output Eye Diagram

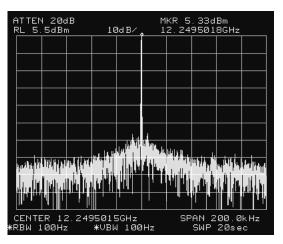

Narrow Band Clock Spectrum

## **CLOCK SPECTRUM**

Wide Band Clock Output Spectrum

**Preliminary Specifications**

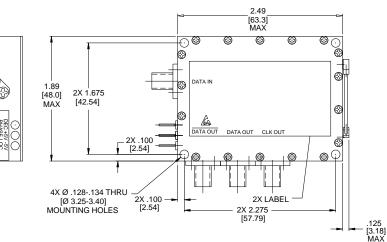

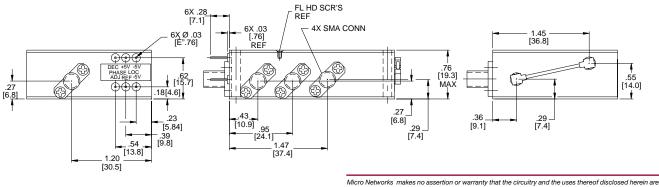

# **ORDERING INFORMATION & MECHANICAL DIMENSIONS**

#### **PIN DESCRIPTIONS**

| Part Number:                          | M830 | <u>x xxxxx.xx</u> x x | Symbol    | Name                             |

|---------------------------------------|------|-----------------------|-----------|----------------------------------|

| Series —                              |      | T T T                 | DATA IN   | Data Input                       |

| No of Inputs —<br>D = Single Input    |      |                       | DATA OUT  | Data Output<br>(non-inverted)    |

| Frequency                             |      |                       | DATA OUT  | Data Output<br>(inverted)        |

| Temperature Range —<br>K = 0 to +70°C |      |                       | CLK OUT   | Clock Output<br>(sinusoidal)     |

| Package Type<br>C = Case/Module Packa | ge   |                       | PHASE ADJ | Phase Shift<br>Adjust            |

|                                       |      |                       | REF       | Decision Threshold<br>Adjustment |

|                                       |      |                       | LOC DEC   | Lock Detect                      |

|                                       |      |                       | +5V       | +5V Power Supply                 |

|                                       |      |                       | -5V       | -5V Power Supply                 |

|                                       |      |                       |           | ·                                |

| Symbol    | Name                              | Description                                                                                              |

|-----------|-----------------------------------|----------------------------------------------------------------------------------------------------------|

| data in   | Data Input                        | AC coupled $50\Omega$ data input                                                                         |

| data out  | Data Output<br>(non-inverted)     | AC coupled 50 $\Omega$ data output                                                                       |

| DATA OUT  | Data Output<br>(inverted)         | AC coupled 50 $\Omega$ data output                                                                       |

| CLK OUT   | Clock Output<br>(sinusoidal)      | AC coupled 50 $\Omega$ clock output                                                                      |

| PHASE ADJ | Phase Shift<br>Adjust             | User input to phase shift the recovered clock over a 100ps range. The control voltage range is 0 to 15V. |

| REF       | Decision Threshold<br>Adjustment  | User input to adjust the decision circuit threshold. The control range is -0.2V to -0.75V.               |

| LOC DEC   | Lock Detect                       | TTL output indicating PLL loss of lock. TTL "1" indicates lock. TTL "0" indicates loss of lock.          |

| +5V       | +5V Power Supply                  | Positive power supply input.                                                                             |

| -5V       | -5V Power Supply                  | Negative power supply input.                                                                             |

| GND       | Power Supply<br>Ground Connection | Ground lug to allow connection of power supply returns to case ground.                                   |

nincro networks makes no assertion or warranty that the circuity and the uses thereor orcicozed neterin are non-infringing on any valid US or foreign patents. Micro Networks assumes no liability as a result of the use of said specifications and reserves the right to make changes to specifications without notice. Contact your nearest Micro Networks sales representative office for the latest specifications.

Micro Networks An Integrated Circuit Systems Company 324 Clark Street = Worcester, MA 01606 = tel: 508-852-5400 = fax: 508-852-8456 European Sales Headquarters = Hertogsingel 20 = 6214 AD Maastricht = The Netherlands = tel: +31-43-32-70912 = fax: +31-43-32-70715 www.micronetworks.com

Micro Networks Corporation Worldwide Headquarters 324 Clark Street • Worcester, MA 01606 • USA tel: 508-852-5400 • fax: 508-852-8456

European Sales Headquarters Hertogsingel 20 = 6214 AD Maastricht = The Netherlands tel: +31-43-32-70912 = fax: +31-43-32-70715

www.micronetworks.com